BEGINNER PROJECT: ShastaPlus IO Pin Toggle

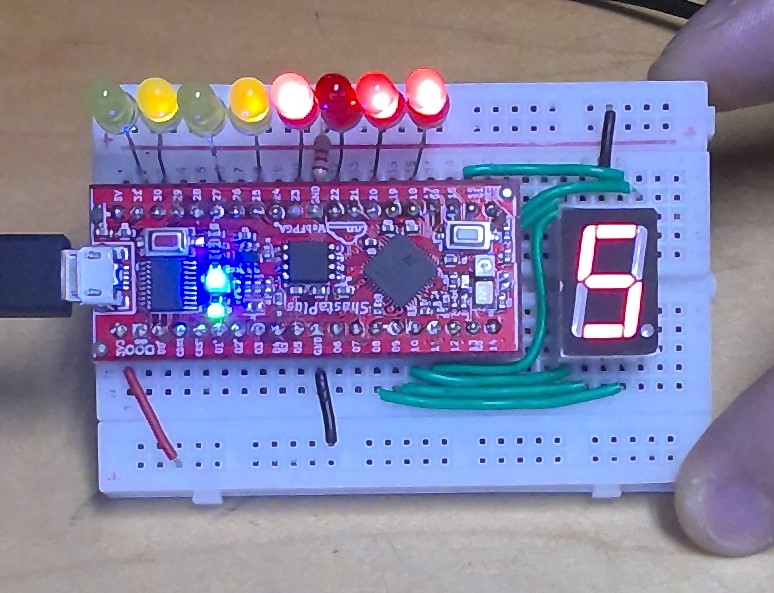

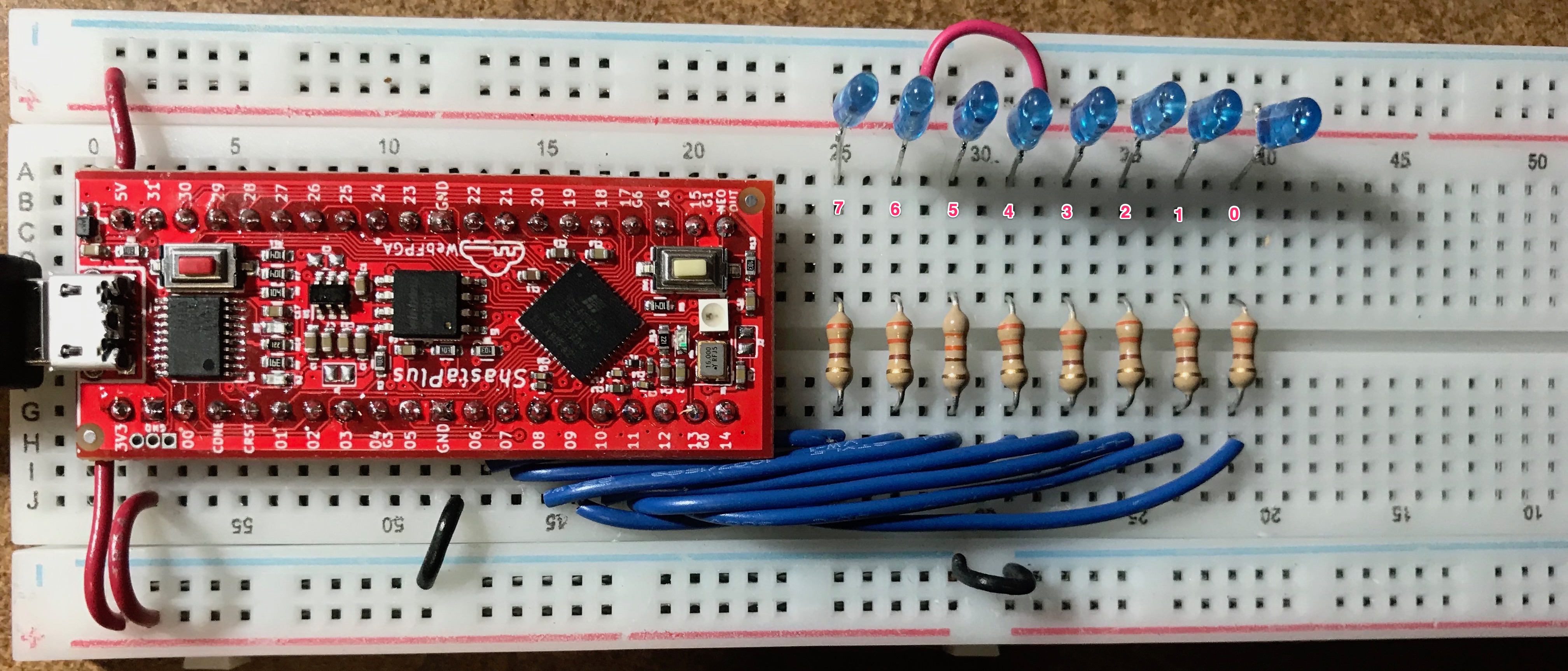

Objective: learn to toggle 1 pc board IO pin, then expand to 8 pins, and drive LEDs. All pins used here are called “User FPGA pins”.

As a beginner I used the Wf_Blinky.v example, online research, and Support Forum help (thank you). Although this project is a “trivial” use of an FPGA, I just wanted to get anything at all to work.

A 16 MHz crystal, external to the FPGA, is the clock source. A 28 bit register (bits 0 - 27) is incremented or decremented, depending on LED wiring, to get a slower count in the higher bits. Bit 24 could be the typical Hello World as it toggles once per second.

The upper 8 counter register bits are routed to pc board pins using @MAP (note the capitalization, I did not at first and nothing worked). Those IO pins are connected to 330Ω current limiting resistors which then connect to blue LED cathodes. The LED anodes connect to the 3.3 volt rail. A LOW or 0 in the corresponding counter register bit will turn a LED ON.

In order to have a LED counter which visually counts up, the counter register must be decremented. On power up the pins seem to all be HIGH (0xFFF FFFF). After the first decrement the counter is 0xFFF FFFE so bit 0 is LOW. If an LED were connected there, it would turn on and off too quickly to see.

Once the decrementing gets to 0xFEF FFFF (1111 1110 1111 1111 1111 1111 1111), bit 20 is LOW so LED_0 turns on, but briefly, for about 1/16 second.

When the count is 0xEFF FFFF (1110 1111 1111 1111 1111 1111 1111), that LOW in bit 24 turns on LED_4, for about 1 second.

The LEDs do work reversed, with their cathodes connected to ground and the anodes connected to the current limiting resistors. To get a visual up-counter, the FPGA counter register needs to be incremented. However, all LEDs are slightly glowing at power up and during flashing, unlike with the other wiring.

In either case the 8 LEDs draw little current, maybe 2 mA per LED. Each blue LED had a measured voltage drop of about 2.7 volts and each resistor about .55 volt

(.55V / 330 ~ 1.7 mA). With all 8 LEDs on the current draw from them would be about 16 mA. Even with such a low current through them, the blue LEDs are quite bright in a fully lit room.

// Toggle one pc board pin for Hello World LED

// rr Sept 1, 2019

// pc board pin 6 connects to 330 ohm resistor which

// connects to LED cathode, LED anode to 3.3 volt rail.

// LED will toggle about once per second

// @MAP_IO LED_0 06

module fpga_top(output wire LED_0, input wire WF_CLK);

reg [27:0] counter;

reg state0;

assign LED_0 = state0;

always @ (posedge WF_CLK) begin

counter <= counter - `b1;

state0 <= counter[24];

end

endmodule

Summary

This text will be hidden

**// ShastaPlus 8 pin toggle, rr Sept 1, 2019**

// PC board pins 06, 07, 08, 09 10, 11, 12, 14 to 330Ω resistors,

// other end of resistors to LED cathodes, LED anodes to 3.3V rail.

// Counter register decrements and rolls over, driven by 16 MHz

// crystal. LEDs show the highest 8 bits in counter register.

// LED_7 toggles slowest; LED_4 toggles about once per second.

// @MAP_IO LED_7 06

// @MAP_IO LED_6 07

// @MAP_IO LED_5 08

// @MAP_IO LED_4 09

// @MAP_IO LED_3 10

// @MAP_IO LED_2 11

// @MAP_IO LED_1 12

// @MAP_IO LED_0 14

module fpga_top(output wire LED_0, output wire LED_1,

output wire LED_2, output wire LED_3, output wire LED_4,

output wire LED_5, output wire LED_6, output wire LED_7,

input wire WF_CLK);

reg [27:0] counter;

reg state0; reg state1; reg state2; reg state3;

reg state4; reg state5; reg state6; reg state7;

assign LED_0 = state0; assign LED_1 = state1;

assign LED_2 = state2; assign LED_3 = state3;

assign LED_4 = state4; assign LED_5 = state5;

assign LED_6 = state6; assign LED_7 = state7;

always @ (posedge WF_CLK) begin

counter <= counter - `b1;

state0 <= counter[20];

state1 <= counter[21];

state2 <= counter[22];

state3 <= counter[23];

state4 <= counter[24];

state5 <= counter[25];

state6 <= counter[26];

state7 <= counter[27];

end

endmodule

Short video clip at: https://www.youtube.com/watch?v=Y3zgIjvGK8E