Is there any chance of getting some documentation on the on-board microcontroller - what commands it responds to via USB, and how one might use it to interact with the FPGA?

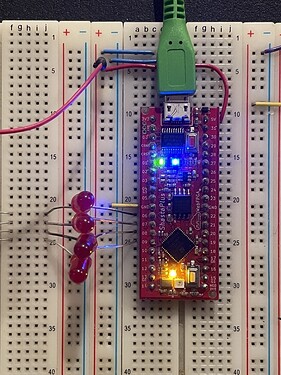

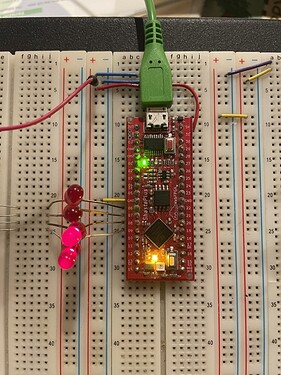

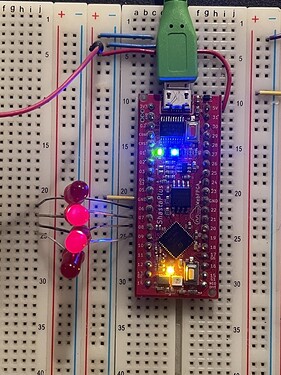

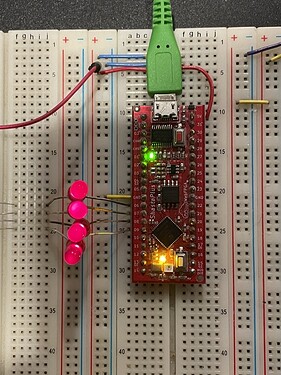

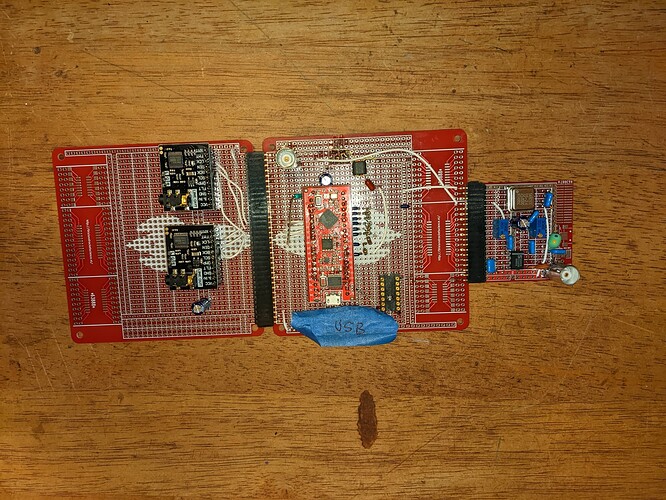

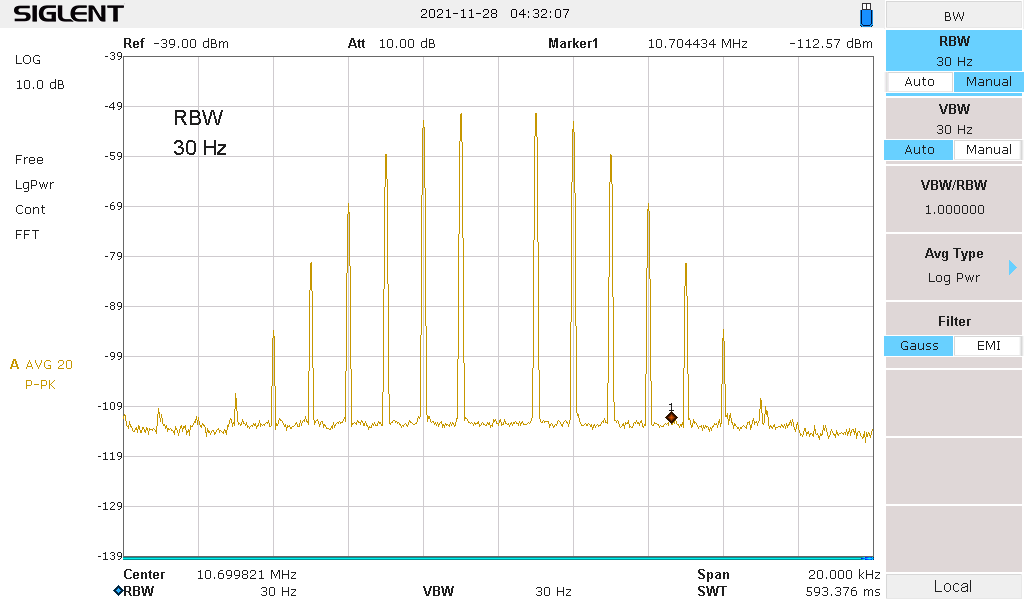

My reason for asking: I’m quite well along in my project, and I have my Shasta board generating 10.7 MHz frequency-modulated RF test signals (multiplex-stereo, for calibrating FM tuners). I’d like to be able to use USB, and the microcontroller interface, as a way of interacting with and reconfiguring the running gateware program (as opposed to having to recompile and flash a modified gateware).

If there’s some reasonable way to get the micro to talk to the FPGA via a serial protocol (SPI or UART-style) I could write the corresponding FPGA logic. Lacking knowledge of what the micro can do, I can’t.

I recall that there was some intention to open-source more of the development toolkit (in particular, the bitstream compression program) - that also would be nice!