Built-in Low Frequency Clock

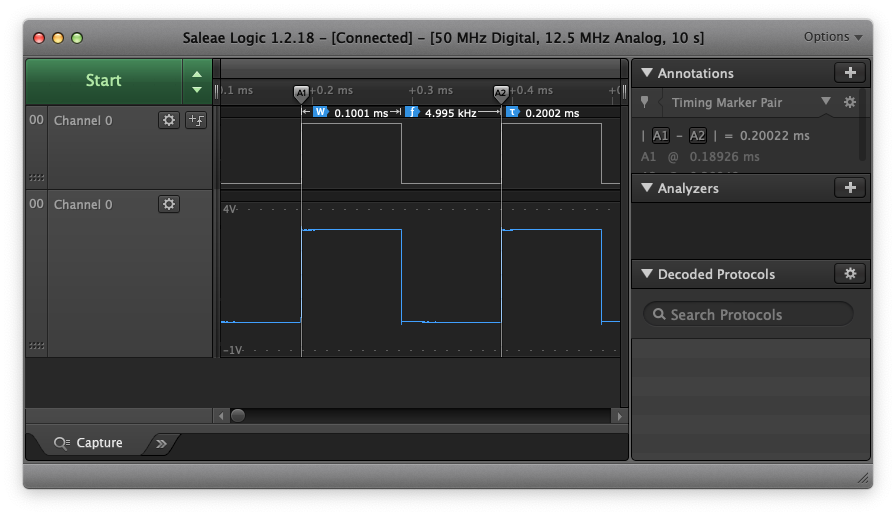

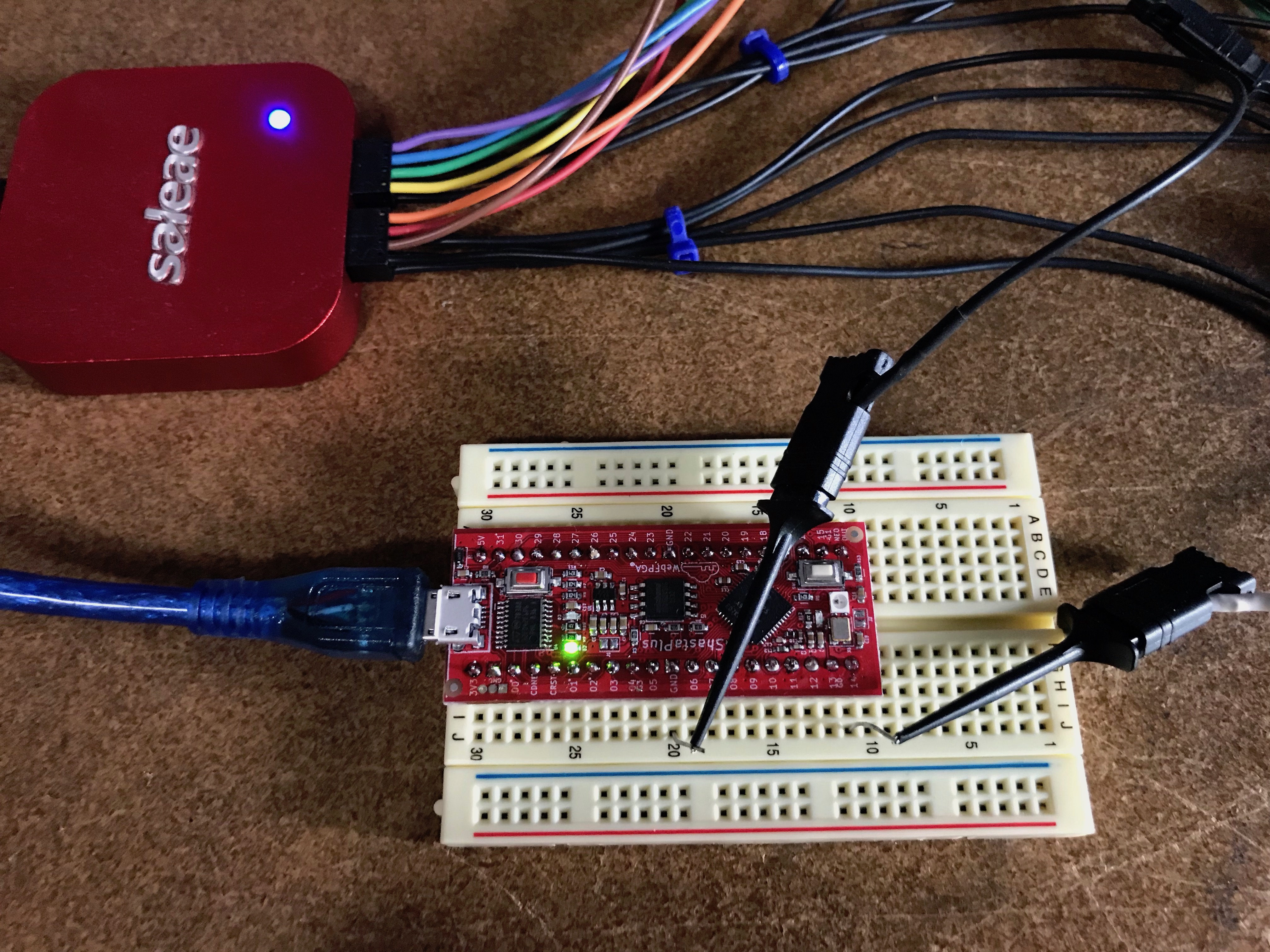

Here is one way to “see” the FPGA low frequency clock.

// ShastaPlus single pin toggle LF OSC, rr Oct 15, 2019

// PC board pin 14 to saleae; PC gnd to saleae gnd

// Pin 14 monitors one half of 10 kHz FPGA oscillator.// @MAP_IO PIN_14 14

module fpga_top(output wire PIN_14);

reg [0:0] counter; reg state0; assign PIN_14 = state0; wire clk_en = 'b1; SB_LFOSC OSC_i ( .CLKLFEN(clk_en), .CLKLFPU(clk_en), .CLKLF(clk)); always @ (posedge clk) begin counter <= counter - 'b1; state0 <= counter; endendmodule

QUESTIONS:

-

Is there a simpler way to output the 10kHz clock to a pin and measure 10 kHz?

-

Is there a better way to declare a 1 bit register?

-

Why does it still synthesize OK with the width omitted in both literals (‘b1)?

-

The synthesis notes say:

Static Timing of Design:

Timing completed. See timing report file.

Clock: OSC_i/CLKLF | Frequency: 257.69 MHz | Target: 0.01 MHz

Why did the synthesizer have such a high frequency of 257 MHz to get to the Target of 10 kHz

(earlier in the notes it started out at 347 MHz)?