As a beginner, here are two confusing things (of many) in this example.

A. Using Logical AND (partial code below)

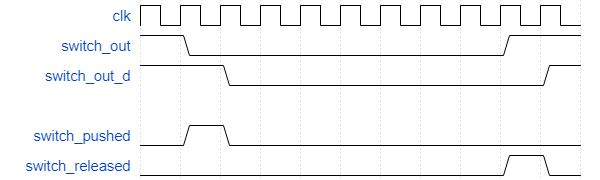

switch_out_d <= switch_out;

endassign switch_pushed = ~switch_out && switch_out_d; assign switch_released = switch_out && ~switch_out_d;

My interpretation (which must be wrong):

Both switch_out and switch_out_d . are 1 bit registers.

switch_out is set as either 0 or 1 depending on whether the 3 bit switch register is 000 or 111.

Then, switch_out_d is set to switch_out, i.e. either 0 or 1

Then, in the logical AND part, these 2 values are equal but one of them is negated before the logical AND.

Which makes me think the results (switch_pushed, switch_released) will always be 0 or false.

Or, maybe there is operator precedence?

B. Concatenation ??

blink_cnt <= { blink_cnt[2:0],blink_cnt[3]}; // rotate a one

I’m thinking this is concatenation. On the first step, blink_cnt is 0001

So the concatenation produces . 001 and 0 to get 0010

The next concatenation produces 010 and 0 to get 0100

And the next: 100 and 0 to get 1000

And the next 000 and 1 to get 0001

Same thing with

if (counter == ( {blink_cnt, 20’h42400} )) begin

because the value in blink_cnt (0001, or 0010, or 0100, or 1000) is concatenated with those lower 20 bits, hex 42400.

So the flashing slows down because a higher and slower bit (21, 22, 23, or 24) is being used for the counter to decide when to toggle the LED or reset counter.